--- 材料科学与工程学院-中文 ---

来源:Nature Electronics

背景概述

将薄原子层沉积电介质与二维 (2D) 半导体集成可用于制造电容等效厚度低于 1 nm 的 2D 晶体管。然而,惰性表面上的原子层沉积和随后的高能金属蒸发产生的不均匀成核可能会使原子薄电介质变得不绝缘。

在这里,南开大学吴金雄研究员团队报告了一种氧化铋辅助化学气相沉积方法来合成具有原子级平坦表面的单晶金属纳米片。纳米片在基板上垂直生长,并且可以通过无聚合物机械压制轻松转移到目标基板上。作者表明,钯纳米片为厚度低于 3 nm 的平面氧化铝 (Al2O3) 和氧化铪 (HfO2) 电介质的原子层沉积提供了优异的表面。然后可以将它们层压到几层二硫化钼 (MoS2) 上作为栅堆叠,电容等效厚度为0.9nm,电容密度约为 3.9μFcm−2。作者的 MoS2 顶栅晶体管采用 2 nm 厚的 Al2O3 或 HfO2 电介质,具有 10−6 A cm−2 的漏电流、约 0.45 V 的低工作电压和小于 1 mV 的迟滞。相关成果以“Vertically grown metal nanosheets integrated with atomic-layer-deposited dielectrics for transistors with subnanometre capacitance-equivalent thicknesses”为题发表在《Nature Electronics》,第一作者为张磊。

图文导读

垂直二维金属的 CVD 生长和表征

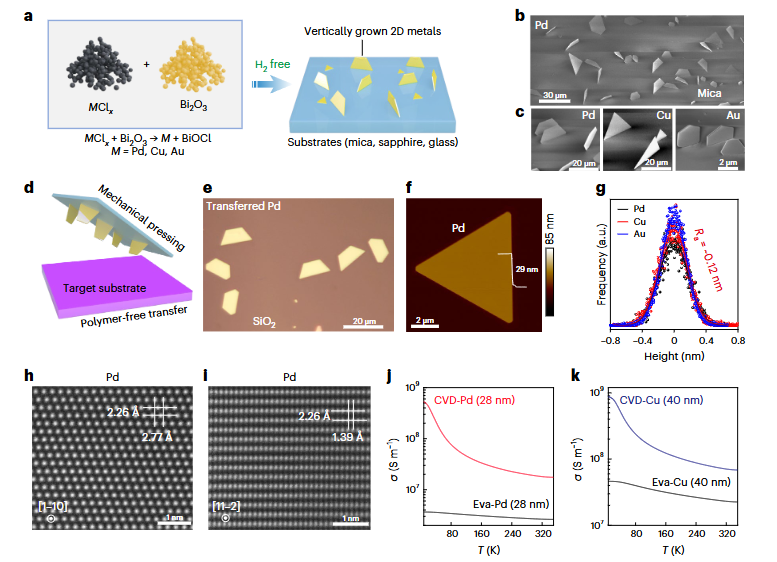

本文开发了一种简单的Bi2O3辅助CVD方法,使用金属氯化物和Bi2O3粉末作为蒸发源(图1a),合成了一系列二维金属单晶(Pd、Cu和Au)。通过优化合成条件,作者在云母基底上合成了三角形或梯形的Pd、Cu和Au二维金属单晶(图1b、c),展示了优选的垂直生长模式。在520°C到540°C的窄温度窗口内,可调整Pd的生长模式。这些二维金属晶体在整个样品上表现出超光滑的表面,可以轻松转移到其他基底上用于不同目的(图1d)。如图1e-g所示,转移后的Pd纳米片保持完好,无皱纹和裂纹。EDX图、XRD和TEM成像(图1h-i)证实了这些二维金属是高质量的面心立方单晶,具有良好的(111)晶体取向。电导率测量显示,CVD生长的二维金属在整个温度范围内的电导率比热蒸发金属高一到两个数量级,在300K时可达107-108 S/m(图1j、k)

图1:垂直生长单晶金属的 CVD 生长、转移和表征

与 ALD 工艺和后续 vdW 集成的兼容性

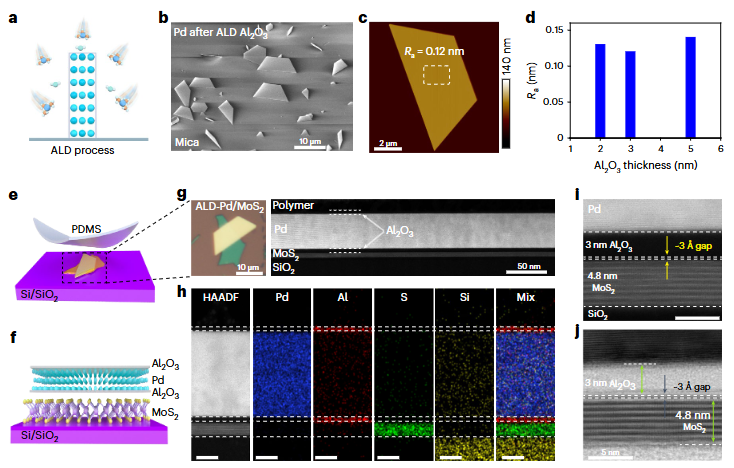

使用垂直生长的二维金属进行栅极控制的关键是成功沉积致密的高κ电介质薄膜且无针孔。ALD是一种常用技术,用于沉积具有原子级厚度精度的超薄高κ电介质。图2a展示了在垂直生长的2D金属上共形沉积超薄Al2O3介电层的ALD工艺示意图。作者主要研究了通过ALD在Pd上沉积高κ电介质的行为,如图2b所示,ALD后Pd纳米片保持了原有的垂直站立形貌,可轻松转移到其他基板上,表面依然原子级平坦。图2c、d展示了沉积不同厚度的Al2O3后的ALD-Pd表面,显示均匀成核。使用PDMS印模可以将ALD-Pd从云母基板上拾取并堆叠到MoS2纳米板上(图2e-g)。高角度环形暗场成像和EDX元素映射证实了堆叠的结构(图2h)。高分辨率图像显示了Al2O3和MoS2之间的小间隙(图2i,j)。这种完美的vdW界面对制造无滞后2D器件至关重要。通过制造使用亚3nm Al2O3(图3)和HfO2(图4)作为顶栅电介质的2D MoS2 FET,成功展示了这种集成。

图2:垂直生长的Pd纳米片的 ALD 兼容性和 vdW 集成

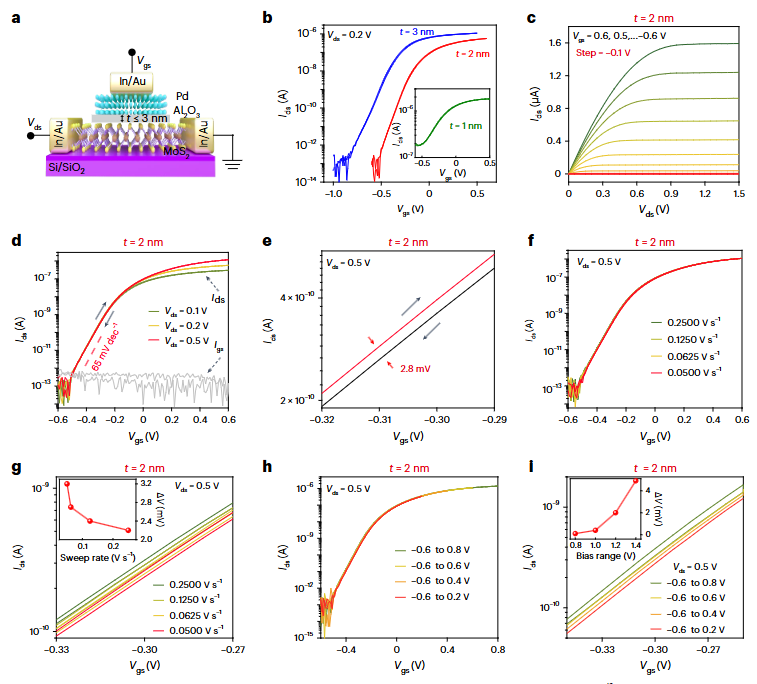

采用亚 3 nm Al 2O3 作为电介质的顶栅 MoS2 FET

图3a展示了具有亚3nm Al2O3介电层的顶栅MoS2 FET的示意图,该器件通过温和对准转移和一步沉积源极、漏极以及In/Au栅极金属在SiO2/Si衬底上制造。通过控制ALD周期(每周期约0.11nm),将Al2O3电介质厚度设置为1、2和3nm。图3b显示了3nm和2nm Al2O3介质的MoS2 FET可以急剧关断至超低关态电流(10−13–10−14 A),但1nm Al2O3绝缘性能减弱。作者重点关注具有2nm Al2O3介质的MoS2 FET的电学测量(图3c-i)。该晶体管在低Vds区域显示线性Ids–Vds曲线,并在大电压范围内饱和,表现出出色的栅极可调性和绝缘性(图3c)。在低工作电压下实现超过107的高开/关比,栅极漏电流超低且几乎与Vgs无关,亚阈值斜率(SS)接近室温下的热极限(图3d)。栅极磁滞约2.8mV(图3e),在不同扫描速率和范围下变化较小(图3f-i)。小滞后现象归因于边界缺陷密度的降低和无晶种层ALD工艺(图3d)。2nm Al2O3门控MoS2 FET的关键因素包括低工作电压(~0.5V)、接近理想的SS值(~65mV/dec)和小栅极磁滞(~1.0mV),这表明一步层压方法形成的优异vdW界面。

图 3 采用亚 3 nm Al2O3/Pd 作为顶栅电介质和电极的 MoS2 晶体管

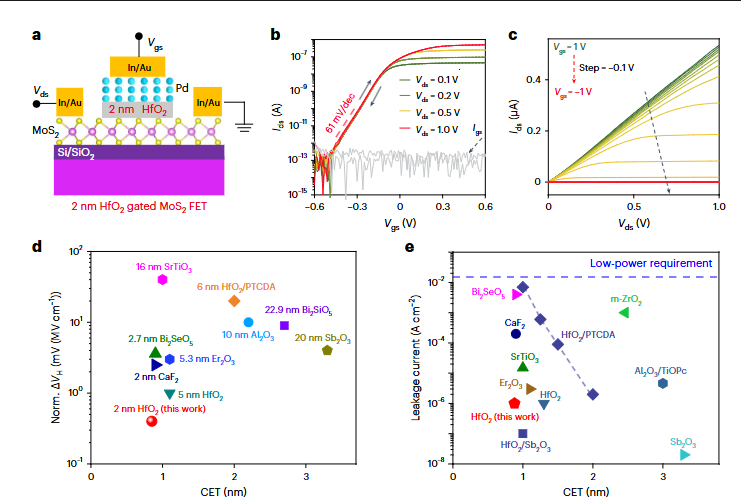

采用 2 nm HfO2 作为电介质的顶栅 MoS2 FET

与 Al2O3 相比,ALD 生长的 HfO2 具有更高的介电常数。基于 MIM 结构的电容-电压 (C-V) 测量证实,ALD 生长的 Al2O3 (39 nm) 和 HfO2 (30 nm) 的介电常数分别为 9.6 和 17.2。集成具有更高 k 值的电介质可以进一步降低 CET。为此,作者制造了一个顶栅 MoS2 晶体管,其厚度为2 nm HfO2,由 SiO2/Si 衬底上垂直生长的 Pd 晶体支撑(图4a)。如图4b所示,该 FET 器件在 ~0.45 V 的小电源电压下工作,具有小亚阈值斜率(~61 mV/dec)、大开/关比>106 和低漏极引起的势垒降低值 (10mV/V)。为了比较 ALD-Pd 门控 MoS2 FET 与其他 2D FET 的性能,作者绘制了栅极磁滞与 CET 的函数关系(图4d),结果显示在 2 nm HfO2 门控 MoS2 FET 中,归一化栅极磁滞小至 0.4 mV/(MV/cm),结合漏电流与 CET 的关系(图4e),该 FET 显示出低栅极磁滞、低漏电流和亚1 nm 的 CET。

图4 :采用 2 nm HfO2/Pd 基作为顶栅电介质和电极的 MoS2 晶体管

总结展望

作者已经证明,光滑的垂直二维金属可以作为使用低于 1 nm CET 的高 κ 氧化物的高质量 ALD 生长平台。通过开发一种Bi2O3 辅助 CVD 方法,作者成功生长了垂直单晶二维金属纳米片(Pd、Au 和 Cu),并可扩展到其他单质金属、二元氧化物和三元含 Bi 化合物。ALD 沉积后,可通过一步工艺将金属氧化物堆叠与 2D 半导体集成,避免了 ALD 技术与 2D 半导体的兼容性问题及顶栅电极沉积的破坏性步骤,为制造亚纳米 CET 的 2D FET 提供了途径。具有清洁表面的 CVD 生长二维金属可以为表面增强拉曼散射、扫描隧道成像和晶面选择催化等基础研究提供材料平台。ALD 氧化物/Pd 的高栅极可调性使其对于创建低功耗器件具有吸引力,并可用于探索二维材料中的奇异现象。

文章信息

期刊:Nature Electronics

题目:Vertically grown metal nanosheets integrated with atomic-layer-deposited dielectrics for transistors with subnanometre capacitance-equivalent thicknesses

作者:Lei Zhang, Zhaochao Liu, Wei Ai, jiabiao Chen, Zunxian lv, Bing Wang, Mingjian Yang, feng Luo &Jinxiong wu

接受日期:July 8 2024

原文链接:https://doi.org/10.1038/s41928-024-01202-3